CR16MCS9

Overview

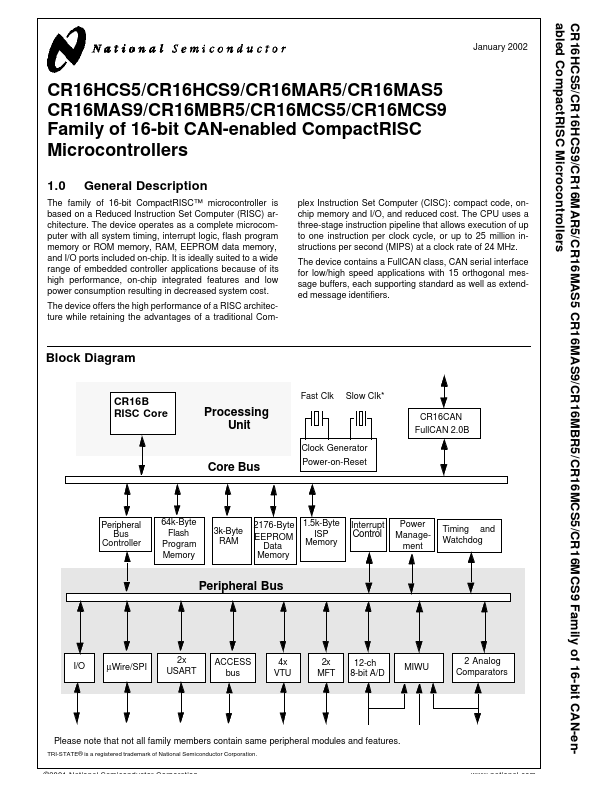

plex Instruction Set Computer (CISC): compact code, onchip memory and I/O, and reduced cost. The CPU uses a three-stage instruction pipeline that allows execution of up to one instruction per clock cycle, or up to 25 million instructions per second (MIPS) at a clock rate of 24 MHz.